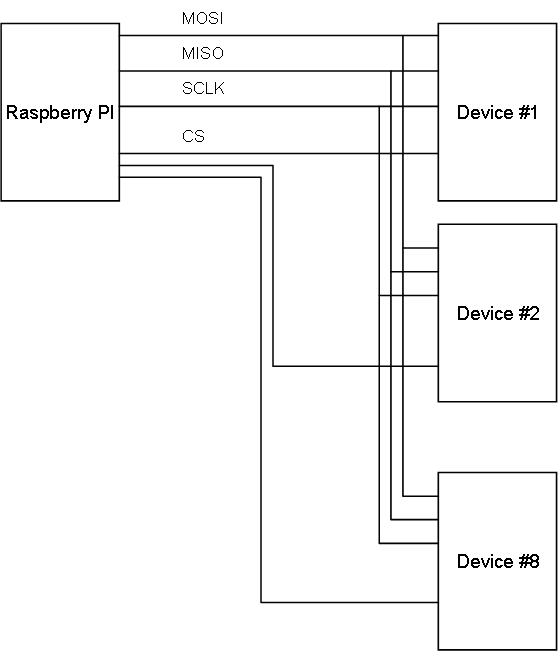

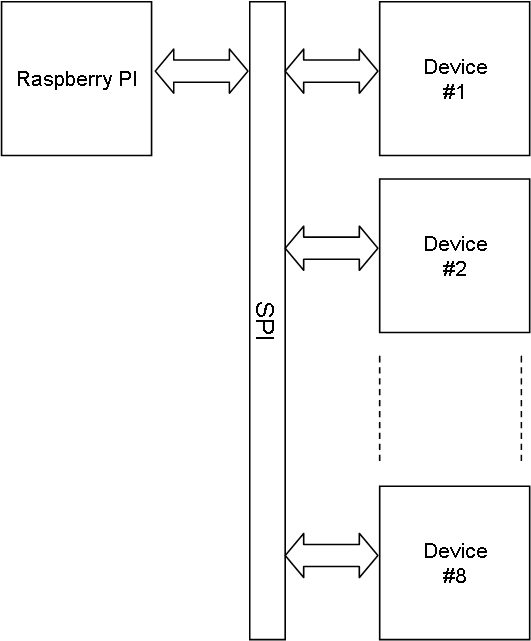

I need a specialized SPI driver to support the Smart SPI concept. The block diagram above show the logical view with device to device communication, while the diagram below show the physical design. Just to remind everyone – in the logical concept we communicate device to device. In the physical this is done by a device sending a message to RPI that send it to the addressed device.

I need a specialized SPI driver to support the Smart SPI concept. The block diagram above show the logical view with device to device communication, while the diagram below show the physical design. Just to remind everyone – in the logical concept we communicate device to device. In the physical this is done by a device sending a message to RPI that send it to the addressed device.

A classic SPI will enable a CS, communicate with that device before it continue to the next device. As discussed before this is not optional as it do not take into account the actual stream queues, so we will implement several important tweaks to optimizeSPI communication efficiency.

We will only use the CS for ID procedures at start-up. I am currently looking into even drop this. Each device here is intelligent and capable of filtering out it’s own messages. They also have 3-state capability allowing them to listen only while only one respond back. This enables a free flow where RPI have a continuous send with a soft-switch selecting the device that communicate back.

This requires specialized SPI drivers both for Raspberry PI and STM32. The advantage for Raspberry PI is that we allow Linux to use deep DMA queues and avoid CPU heavy bit-banging. The only dissadvantage is a complex SPI driver.

My current Hat’s support CS addressing using a classic address selection. I am considering ditching that and set the MCU address directly with 3-4 GPIO pins. The drawback is that I need to modify all Hat’s, but that is doable since none are in production yet – and I am commiting to using a number of pin’s for address setting. The usage will be the same as before, but we drop the SPI ID procedure because it is not needed anymore. At precent I will focus on a single Hat, so I can pick up this as I make the next revision of the Hat’s. It also gives me time to mature this change a bit.